实验原理与相关准备

七段数码管是电子开发过程中常用的输出显示设备。实验箱中七段数码管采用共阴极,当数码管的中的哪一个段被输入高电平,则相应的这一段被点亮。四位一体的七段数码管在单个静态数码管的基础上加入了用于选择哪一位数码管的位选信号端口。

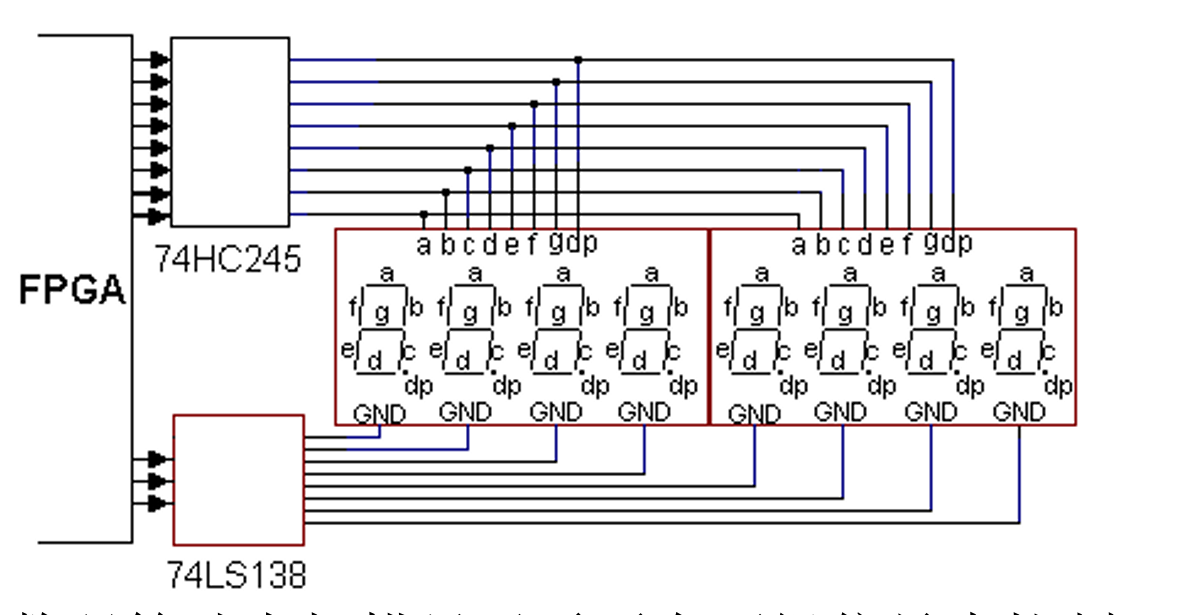

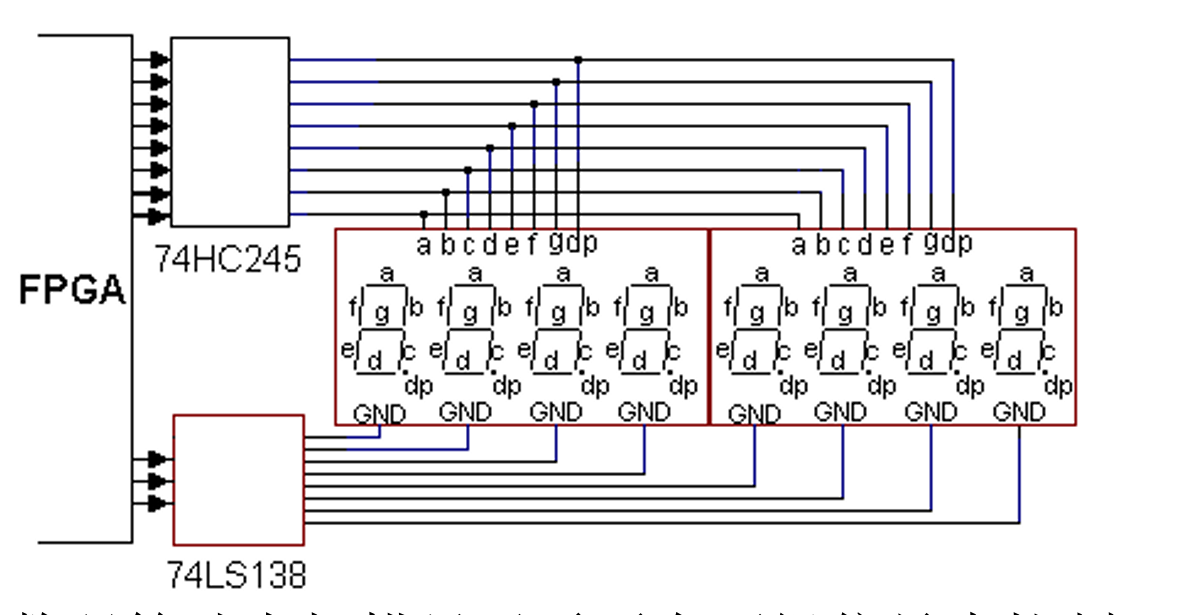

八个数码管的a、b、c、d、e、f、g、h、dp都连在了一起,8个数码管分别由各自的位选信号来控制,被选通的数码管显示数据,其余关闭。这样对于一组数码管动态扫描显示需要有两组信号来控制:一组是字段输出口输出的字形代码,用来控制显示的字形,称为段码;另一组是位输出口的控制信号,用来选择第几个数码管工作,称为位码。

实验内容及过程

本实验要求完成的任务是在时钟信号的作用下,通过输入的键值在数码管上显示相应的键值。

在实验调试中,数字时钟从1HZ 开始改变,频率逐步提高,观察当始终频率达到多少时,可以看到8个数码管稳定的输出。

用四个拨动开关作为输入,当四个拨动开关置为一个二进制数时,在数码管上显示其十六进制的值。

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

| library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity lab5 is

port(

clk : in std_logic;

key : in std_logic_vector(3 downto 0);

ledag: out std_logic_vector(6 downto 0);

sel : out std_logic_vector(2 downto 0)

);

end lab5;

architecture behaviour of lab5 is

signal count : std_logic_vector(2 downto 0) := "000";

begin

process(clk)

begin

if rising_edge(clk) then

count <= count + 1;

end if;

end process;

sel <= count;

process(key)

begin

case key is

when "0000" => ledag <= "0111111";

when "0001" => ledag <= "0000110";

when "0010" => ledag <= "1011011";

when "0011" => ledag <= "1001111";

when "0100" => ledag <= "1100110";

when "0101" => ledag <= "1101101";

when "0110" => ledag <= "1111101";

when "0111" => ledag <= "0000111";

when "1000" => ledag <= "1111111";

when "1001" => ledag <= "1101111";

when "1010" => ledag <= "1110111";

when "1011" => ledag <= "1111100";

when "1100" => ledag <= "0111001";

when "1101" => ledag <= "1011110";

when "1110" => ledag <= "1111001";

when "1111" => ledag <= "1110001";

when others => ledag <= "0000000";

end case;

end process;

end behaviour;

|