这是一个简易的1khz输入频率的电子钟。简易数字钟电路分两个层次:

1.先设计底层的24进制和60进制模块 60进制模块:

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 library IEEE;use IEEE.STD_LOGIC_1164.ALL ;use IEEE.NUMERIC_STD.ALL ;entity counter_60 is Port ( clk : in STD_LOGIC ; reset : in STD_LOGIC ; count : out STD_LOGIC_VECTOR (7 downto 0 ); carry : out STD_LOGIC ); end counter_60;architecture Behavioral of counter_60 is signal cnt : integer range 0 to 59 := 0 ; begin process (clk, reset) begin if reset = '1' then cnt <= 0 ; carry <= '0' ; elsif rising_edge(clk) then if cnt = 59 then cnt <= 0 ; carry <= '1' ; else cnt <= cnt + 1 ; carry <= '0' ; end if ; end if ; end process ; count <= std_logic_vector (to_unsigned(cnt / 10 , 4 ) & to_unsigned(cnt mod 10 , 4 )); end Behavioral;

24 进制模块:

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 library IEEE;use IEEE.STD_LOGIC_1164.ALL ;use IEEE.NUMERIC_STD.ALL ;entity counter_24 is Port ( clk : in STD_LOGIC ; reset : in STD_LOGIC ; count : out STD_LOGIC_VECTOR (7 downto 0 ); carry : out STD_LOGIC ); end counter_24;architecture Behavioral of counter_24 is signal cnt : integer range 0 to 23 := 0 ; begin process (clk, reset) begin if reset = '1' then cnt <= 0 ; carry <= '0' ; elsif rising_edge(clk) then if cnt = 23 then cnt <= 0 ; carry <= '1' ; else cnt <= cnt + 1 ; carry <= '0' ; end if ; end if ; end process ; count <= std_logic_vector (to_unsigned(cnt / 10 , 4 ) & to_unsigned(cnt mod 10 , 4 )); end Behavioral;

2.设计 1Khz->1Hz 的分频模块 分频器:

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 library IEEE;use IEEE.STD_LOGIC_1164.ALL ;use IEEE.NUMERIC_STD.ALL ;entity freq_divider is Port ( clk_in : in STD_LOGIC ; reset : in STD_LOGIC ; clk_out : out STD_LOGIC ); end freq_divider;architecture Behavioral of freq_divider is constant N : integer := 1000 ; signal count : integer range 0 to N/2 -1 := 0 ; signal clk_div : STD_LOGIC := '0' ; begin process (clk_in, reset) begin if reset = '1' then count <= 0 ; clk_div <= '0' ; elsif rising_edge(clk_in) then if count = N/2 -1 then count <= 0 ; clk_div <= not clk_div; else count <= count + 1 ; end if ; end if ; end process ; clk_out <= clk_div; end Behavioral;

3.设计动态扫描模块 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 library IEEE;use IEEE.STD_LOGIC_1164.ALL ;use IEEE.NUMERIC_STD.ALL ;entity dynamic_scan is Port ( clk_scan : in STD_LOGIC ; reset : in STD_LOGIC ; digits : in STD_LOGIC_VECTOR (23 downto 0 ); seg : out STD_LOGIC_VECTOR (6 downto 0 ); sel : out STD_LOGIC_VECTOR (2 downto 0 ) ); end dynamic_scan;architecture Behavioral of dynamic_scan is signal scan_count : unsigned (2 downto 0 ) := (others => '0' ); signal current_digit : STD_LOGIC_VECTOR (3 downto 0 ); begin process (clk_scan, reset) begin if reset = '1' then scan_count <= (others => '0' ); elsif rising_edge(clk_scan) then if scan_count = 7 then scan_count <= (others => '0' ); else scan_count <= scan_count + 1 ; end if ; end if ; end process ; sel <= std_logic_vector (scan_count); process (scan_count, digits) constant DASH : STD_LOGIC_VECTOR (3 downto 0 ) := "1010" ; begin case to_integer(scan_count) is when 0 => current_digit <= digits(7 downto 4 ); when 1 => current_digit <= digits(3 downto 0 ); when 2 => current_digit <= DASH; when 6 => current_digit <= digits(15 downto 12 ); when 7 => current_digit <= digits(11 downto 8 ); when 5 => current_digit <= DASH; when 3 => current_digit <= digits(23 downto 20 ); when 4 => current_digit <= digits(19 downto 16 ); when others => current_digit <= "0000" ; end case ; end process ; process (current_digit) begin case current_digit is when "0000" => seg <= "0111111" ; when "0001" => seg <= "0000110" ; when "0010" => seg <= "1011011" ; when "0011" => seg <= "1001111" ; when "0100" => seg <= "1100110" ; when "0101" => seg <= "1101101" ; when "0110" => seg <= "1111101" ; when "0111" => seg <= "0000111" ; when "1000" => seg <= "1111111" ; when "1001" => seg <= "1101111" ; when "1010" => seg <= "1000000" ; when others => seg <= "0000000" ; end case ; end process ; end Behavioral;

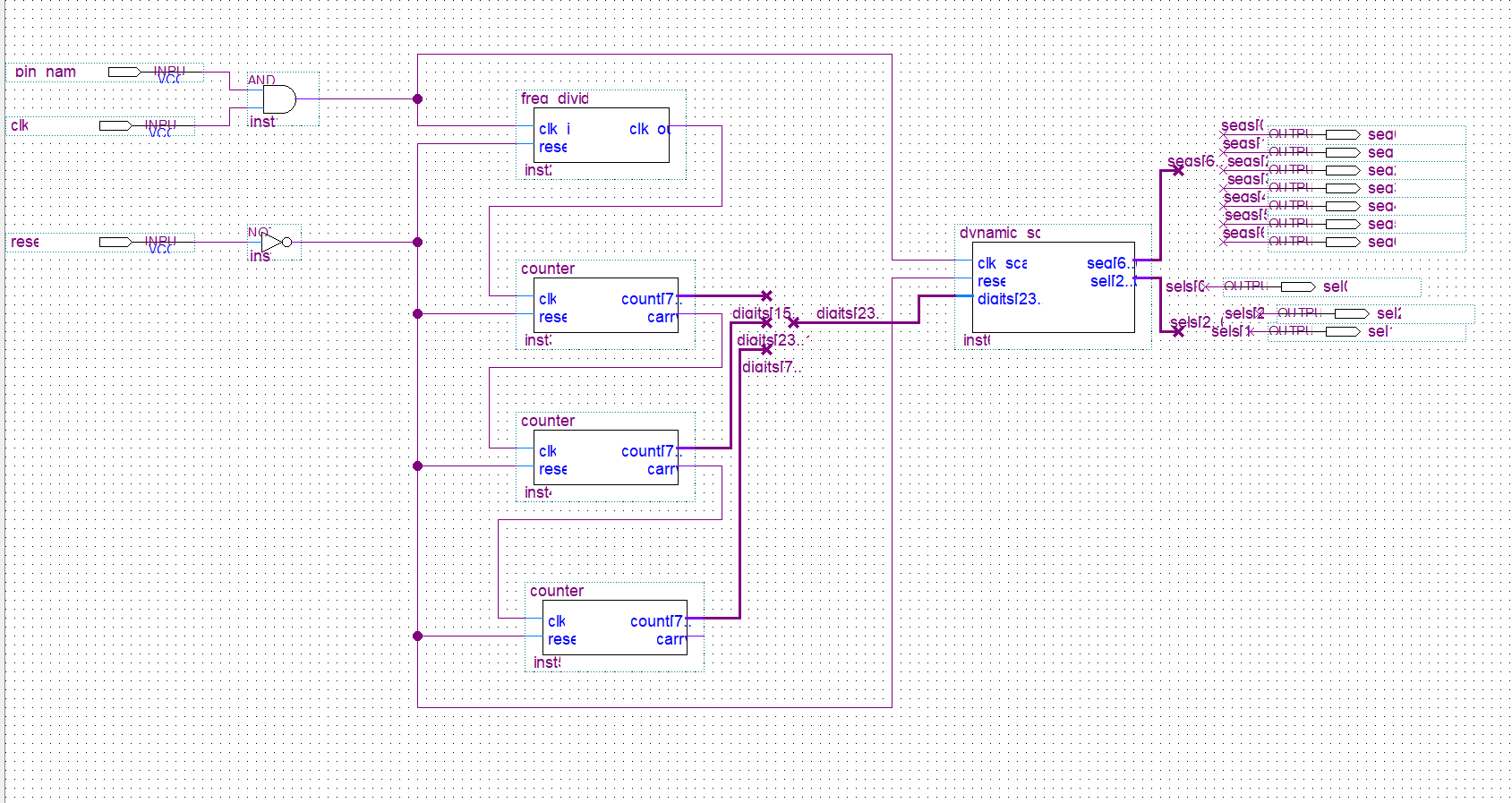

4.编译模块,获得组件;使用原理图调用上述模块,设计电子钟的顶层模块

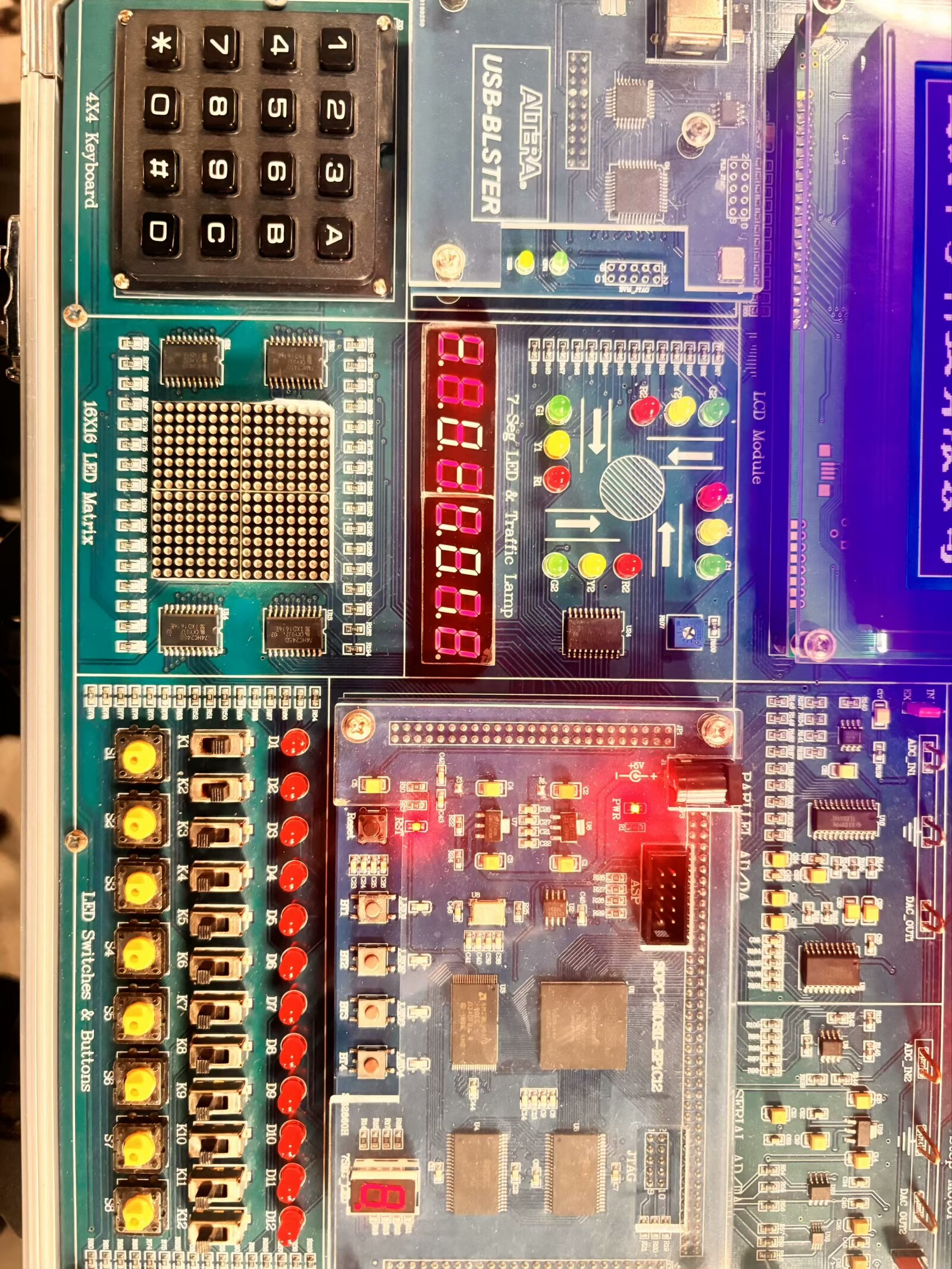

实验结果: